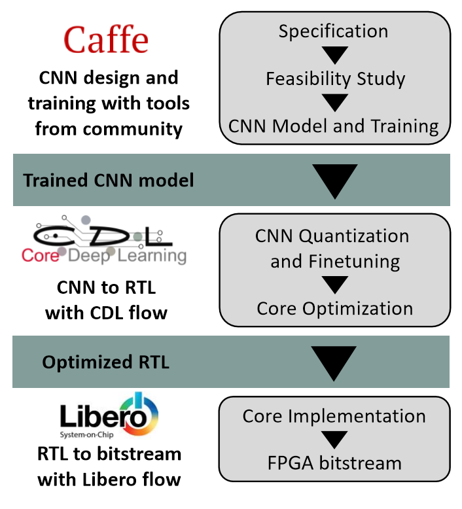

How to Develop High-Performance Deep Neural Network Object Detection/Recognition Applications for FPGA-based Edge Devices - Embedded Computing Design

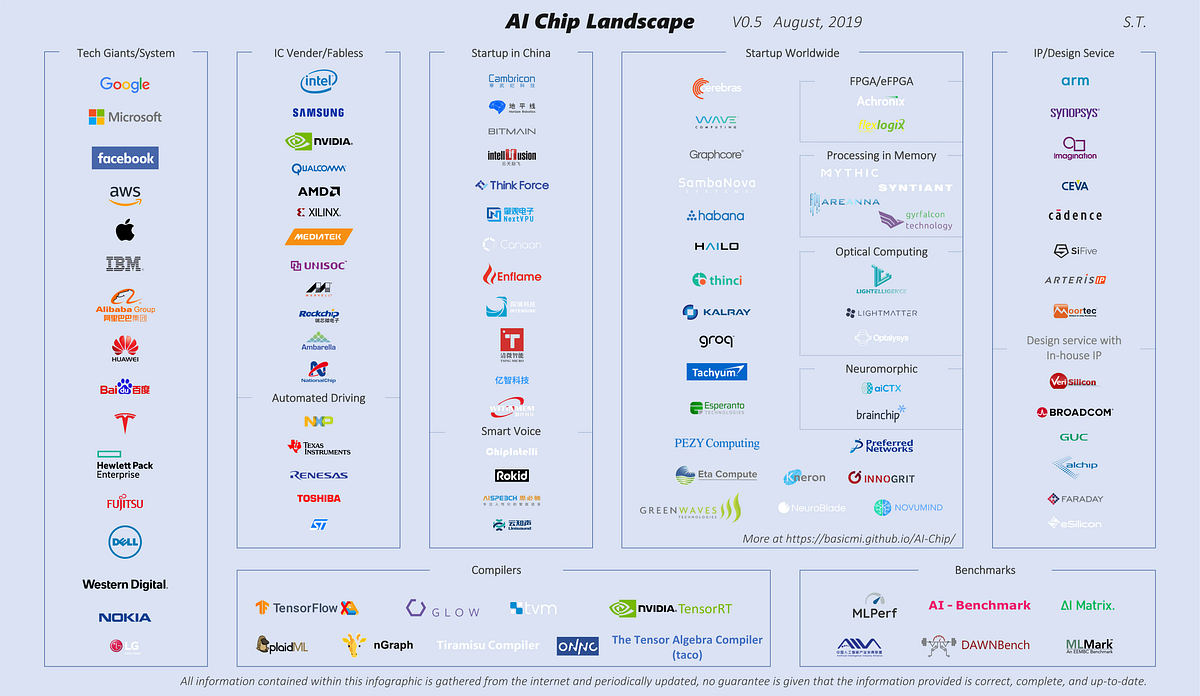

Analog architectures for neural network acceleration based on non-volatile memory: Applied Physics Reviews: Vol 7, No 3

Intel Speeds AI Development, Deployment and Performance with New Class of AI Hardware from Cloud to Edge | Business Wire